# A Balanced Ka-Band GaAs FET MMIC Frequency Doubler

Mohammed Abdo-Tuko, Ralf Bertenburg, and Ingo Wolff, *Fellow, IEEE*

**Abstract**—A simplified and miniaturized state-of-the-art balanced GaAs FET MMIC frequency doubler operating at 36 GHz has been designed and realized in coplanar waveguide technology. The passive part of the circuit is designed using an effective, in-house developed quasi-static finite-difference method for the analysis of coplanar structures [1], [2] while the active device is characterized by using the Curtice-Ettenberg model [3]. The model makes use of the measured electrical values of the transistor and interprets them through approximate empirical formulas. The results obtained demonstrate that by using simple models, which require very little computation time, it is possible to design an efficient frequency doubler in the Ka-band with a maximum conversion gain of 3 to 6 dB, without the need of using complicated transistor models or circuitry.

## I. INTRODUCTION

THE COPLANAR technology has attracted the attention of many MMIC designers in the recent years [4]–[7]. This is because it has the advantage of being truly planar and thus provides the possibility of on-wafer circuit tests, it permits easy connection of both series and shunt circuit elements, and it has low radiation losses in the odd mode. Moreover, CPW parameters are not sensitive functions of substrate thickness, and a wide range of impedance is achievable on reasonably thick substrates. These advantages can be assured only if a thorough investigation of the associated coplanar discontinuities such as  $T$ -junctions, bends, cross-junctions, and air-bridges is done and their effects are taken into account in the design. To characterize these discontinuities, accurate lumped element equivalent circuit models [1], [5] have been used. The balanced frequency doubler presented here is designed by taking the above mentioned effects into consideration. The discrepancy between simulation and measurement results obtained is within the limit of design tolerance.

## II. ANALYSIS AND DESIGN METHOD

In analyzing and designing a FET frequency doubler, the attention of the designer usually concentrates around the following two points:

- 1) The equivalent circuit model parameters of the FET must be determined from measurement values, something that cannot be done analytically.

- 2) The preconditions necessary for optimum doubler operation (such as dc bias, excitation level, and impedance matching) must be fulfilled.

Manuscript received January 6, 1994.

The authors are with the University of Duisburg, 47048 Duisburg, Germany.

IEEE Log Number 9402172.

Regarding the first point, the parameters of the chosen transistor model (Curtice-Ettenberg model in our case) is determined and optimized by minimizing the discrepancy between the measured and simulated DC and RF quantities at every operating point. Regarding the second point, the following conditions can be used as a basis to set optimization criteria for doubler design:

- 1) One maximizes the ratio of the second-harmonic and the fundamental frequency power at the output, i.e.  $P_{\text{out}}(2\omega_0)/P_{\text{out}}(\omega_0)$ , so that one obtains an output signal with maximum second harmonic distortion; or

- 2) one forms the ratio between the second harmonic power at the output and the fundamental power at the input, i.e.  $P_{\text{out}}(2\omega_0)/P_{\text{in}}(\omega_0)$ , thereby maximizing or minimizing the resulting conversion gain or loss, respectively, as the case may be.

Regarding bias point, it has been theoretically and experimentally verified [8] that it is the variation of the gate-source voltage  $V_{\text{gs}}$  that has greater effect in causing nonlinear distortion, thus generating a waveform that is rich in second harmonic component. Assuming a constant value of  $V_{\text{ds}}$ , the drain current can be approximated as [3]:

$$i_{\text{ds}} = a'_0 + a'_1 v_{\text{gs}}^2 + a'_2 v_{\text{gs}}^2 + a'_3 v_{\text{gs}}^3, \quad (1)$$

where  $v_{\text{gs}}$  contains both the dc and ac voltage components of the input.

The coefficients  $a'_0, a'_1, a'_2, a'_3$  are the Curtice-Ettenberg model parameters, where the effect of the tangent hyperbolic function in the model [3] has also been included.

Expressing  $v_{\text{gs}}$  as  $v_{\text{gs}} = V_{\text{gs}0} + V_{\text{gs}1} \cos(\omega t)$ , it can be shown that the optimum gate bias voltage  $V_{\text{gs}0}$ , necessary for optimum generation of the second harmonic is given by:

$$V_{\text{gs}0} = -\frac{1}{3} \left( \frac{a'_2}{a'_3} \right) + \sqrt{\frac{1}{4} V_{\text{gs}1}^2 + \frac{1}{3} \left( \frac{a'_1}{a'_3} \right) - \frac{1}{9} \left( \frac{a'_2}{a'_3} \right)^2} \quad (2)$$

This optimum voltage usually lies near pinch-off.

The balanced frequency doubler of the type proposed here basically consists of a pair of identical GaAs FET's, a  $180^\circ$  phase-shifting circuit designed using proper combination of spiral inductors, power splitter/combiner circuits, and impedance matching networks. The gates of the two transistors are driven by signals having a  $180^\circ$  phase difference, and this results in the mutual cancellation of the fundamental signals at the output while the second-harmonic signals combine and add up.

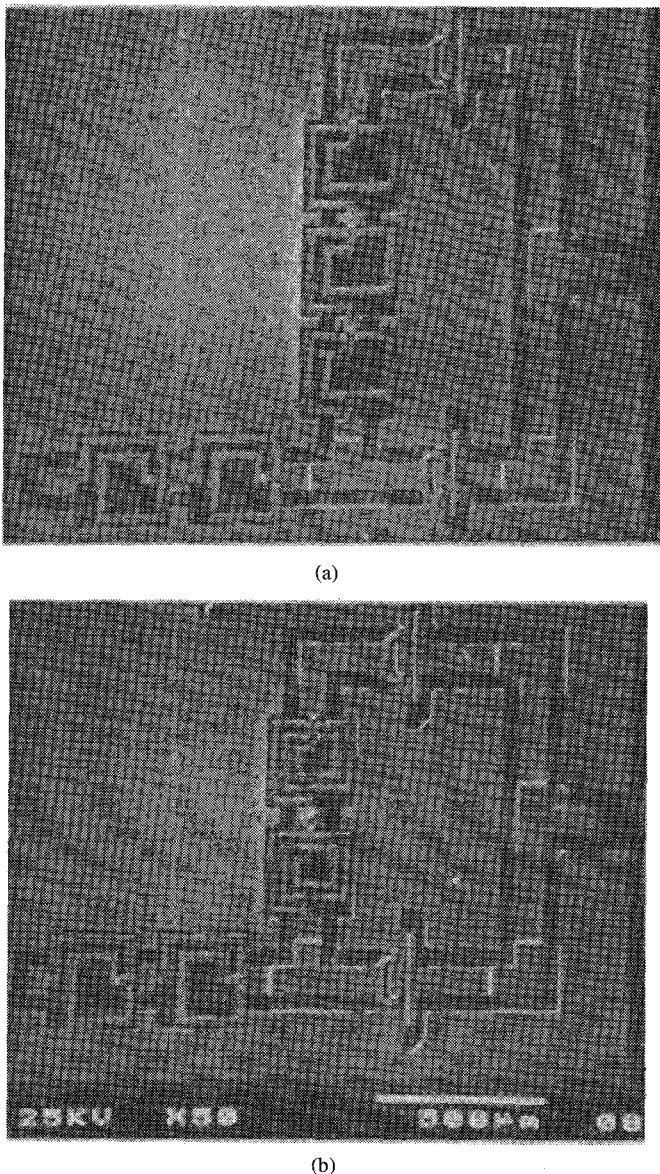

Fig. 1. (a) Photograph of the 36-GHz balanced MMIC frequency doubler, where three spiral inductors connected in series are used as the phase-shifting circuit. (b) Photograph of the 36-GHz balanced MMIC frequency doubler, where two spiral inductors connected in series are used as the phase-shifting circuit.

Fig. 1 shows the REM photograph of two versions of the realized balanced doubler. The first one (Fig. 1(a)) utilizes three spiral inductors (of 1.5 turns each) connected in series for the purpose of phase shifting, and the second one (Fig. 1(b)) uses only two spiral inductors, also connected in series, having 2.5 turns each. Simulation and measurement results showed that both doublers have identical performance. Obviously, the doubler with two spiral inductors has the advantage of being more compact ( $1.5 \text{ mm} \times 1.5 \text{ mm}$ ) and is, therefore, preferable for fabrication. On the other hand, the use of the 1.5-turn spiral inductor has the advantage of providing more capacitance to ground, which is usually necessary for impedance matching purposes. Moreover, its first resonant frequency is higher than the 2.5-turn inductor and, therefore, there is much less danger that this resonant frequency falls in the frequency range at which the circuit is desired to operate.

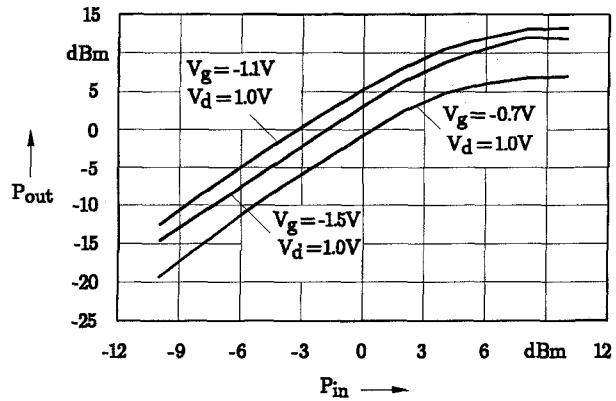

Fig. 2. Simulated second-harmonic output power as a function of the input power for different bias voltages of the transistor.

A new approach in coplanar technique is used for the design of the required impedance matching and phase-shifting circuits in that the parasitic capacitances of spiral inductors and the effects of the coplanar discontinuities have been fully exploited in the design. In this way, the conventionally used and space occupying  $180^\circ$  couplers, as well as the MIM capacitors, have been effectively eliminated. For the simulation, the coplanar line discontinuities and the spiral inductors are substituted by their lumped element equivalent circuits [5] and the transistors by the Curtice-Ettenberg nonlinear transistor model. The transistor type used for the design is a GaAs FET with  $0.3 \mu\text{m}$  gate length and  $200 \mu\text{m}$  gate width fabricated in coplanar technology at the Semiconductor Department of the University of Duisburg [9]. The overall circuit is simulated using a commercially available CAD harmonic balance simulator [10].

### III. RESULTS

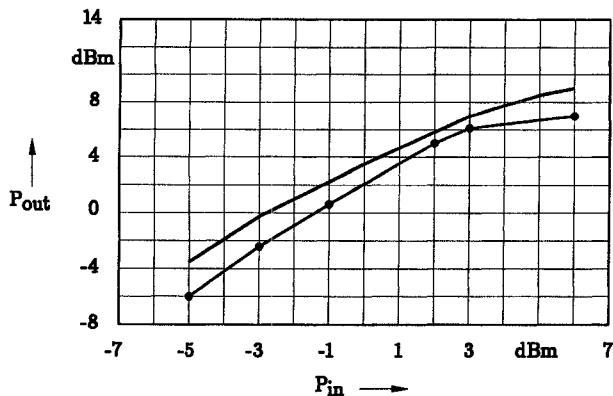

To observe the effect of the bias voltage on the performance of the doubler, the output power is simulated for different operating point of the transistor. This is shown in Fig. 2, where the simulated dependence of the second-harmonic output power on the input power with the bias voltage taken as a parameter is drawn. The optimum operating gate voltage of the transistor is found to be  $-1.1 \text{ V}$ . It is worth mentioning that, whereby the optimum bias point is sensitive to the variation of the gate voltage, it is not so to the variation of the drain voltage. To help compare the simulation results with the measurement results obtained, it makes sense to first re-simulate the circuit using the transistor parameters obtained from newly measured data of the transistor that is found on the wafer on which the whole doubler circuits is fabricated. The measured performance of the doubler is then compared with the newly simulated results. Fig. 3 shows the measured and the newly simulated output power of the doubler. The realized doubler has a conversion gain of  $3 \text{ dB}$ . This result is significant because doublers reported so far in this frequency range usually have conversion losses. Moreover, they do not take coplanar discontinuities into account and that makes our design approach unique. The doubler has a bandwidth of 3 to 4 GHz. However, the center frequency of the realized doublers has shifted by 2 to 3 GHz from the design value (36 GHz). This frequency shift can be

Fig. 3. Measured (dotted line) and simulated (solid line) output power of the 36-GHz balanced MMIC frequency doubler as a function of the input power.

attributed, among other things, to the technological difficulty in reproducing the transistor parameters accurately (after all the transistors used here are not industry products; they are, rather, fabricated at our university for research purposes). The fact that a simplified transistor model is used for the simulation also contributes to the discrepancy between measurement and calculation results. Nevertheless, the operating frequency lies within the design bandwidth of the circuit.

#### IV. CONCLUSION

A new CAD-based approach in the design of GaAs FET balanced frequency doubler has been applied in coplanar techniques. The design method exploits the parasitic effects of spiral inductors and coplanar line discontinuities in the

design of the impedance-matching and phase-shifting circuits. A simplified transistor model has been used for the nonlinear simulation. Measurement results have verified the validity of the design approach used.

#### REFERENCES

- [1] M. Naghed and I. Wolff, "Equivalent capacitances of coplanar waveguide discontinuities and interdigitated capacitors using a three-dimensional finite difference method," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-38, no. 12, pp. 1808-1815, Dec. 1990.

- [2] M. Naghed, M. Rittweger, and I. Wolff, "A new method for the calculation of equivalent inductances of coplanar waveguide discontinuities," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 1991, pp. 747-750.

- [3] W. R. Curtice and M. Ettenberg, "A nonlinear GaAs FET model for use in the design of output circuits for power amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, no. 12, pp. 1383-1293, Dec. 1985.

- [4] M. Abdo-Tuko and I. Wolff, "Novel 36 GHz GaAs FET frequency doublers using (M)MIC coplanar technology," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 1992, pp. 1167-1170.

- [5] M. Abdo-Tuko, M. Naghed, and I. Wolff, "Novel 18/36 GHz (M)MIC GaAs FET frequency doublers in CPW-techniques under the consideration of coplanar discontinuities," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-41, no. 12, Aug. 1993.

- [6] D. F. Williams and S. E. Schwarz, "Design and performance of coplanar waveguide bandpass filters," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, no. 7, pp. 558-566, July 1983.

- [7] H. Ogawa and A. Minagawa, "Unipolar MIC balanced multiplier—A proposed new structure for MIC's," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-35, no. 12, pp. 1363-1368, Dec. 1987.

- [8] G. S. Dow and L. S. Rosenheck, "A new approach for mm-wave generation," *Microwave J.*, pp. 147-162, Sept. 1983.

- [9] R. Bertenburg, "Technologie kopplanarer monolithisch integrierter Mikrowellen-schaltungen auf Galliumarsenid unter Verwendung von Submikron-Feld-effekttransistoren," Ph.D. dissertation (in German), University of Duisburg, July 1992.

- [10] "Program Touchstone/Libra," Version 3.1, EEsol, Inc., Westlake Village, CA 91362.